#### Abstract

The goal of this project is to design a multiple microcontroller electronic control system (MMECS) that would be used to control future robots. In specific, this project is to recommend appropriate microcontrollers and communication protocols to fit into the given system architecture. The motivation for designing the MMECS is to overhaul the wiring problems that are faced in the development of the previous robots and to make the control system modular for the ease of the users developing the robot as well as to have a framework to allow for future upgrades to the electronic control system. The project approaches this problem by performing a market search for suitable microcontrollers, followed by performing an analysis of the communication protocols. The project then uses the results from the analysis of communication protocols and matches the analysis results with the shortlisted microcontrollers to obtain a suitable combination is chosen to meet the requirements of the MMECS.

The following are the recommendations for the MMECS:

#### Microcontrollers

Main Microcontroller:

i.MX31 from Freescale

Communications Microcontroller: LPC2194/01 from NXP

Low Level Microcontroller: LPC2194/01 from NXP

#### Communication Protocols

Main and Communications Microcontroller: Full Speed USB

o Communications and Low Level Microcontroller: CAN Bus

# **Executive Summary**

Over the course of the past year, this Masters of Engineering design project has been working on a task to design a multiple microcontroller electronic control system (MMECS) that would be used for controlling walking robots that will be built in the Biorobotics and Locomotion Laboratory under Professor Andy Ruina.

This project approaches MMECS with 2 key tasks. The first is to choose suitable microcontrollers that would fit the requirements of the MMECS and the second is to determine the most appropriate communications protocol for communication between the multiple microcontrollers in the system.

After performing a market search for suitable protocols and the analysis of promising communications protocols, a recommended design is obtained for the MMECS. The setup recommended in this project not only fulfills the technical requirements of the project by meeting key parameters, it also takes into account the personnel and technical skill level of the research lab as well. In addition, the design, choice of microcontrollers and communication protocols also allows for scalability to accommodate a larger system if necessary and upgradability to allow incremental changes to take place over time on the electronic control system.

## 1. Introduction

#### 1.1. Motivation

The motivation for designing a new electronic control system is threefold. Firstly, we hope to be able to implement a modular system of design for the electronic components. From our previous experiences of designing the Cornell Ranger as well as the Marathon Walker Bot (MWB), where the electronic components were integrated in a less modular manner, the programmers often had difficulty finding bugs in the code when a programming error was suspected. A less modular system also leads to a small group doing most of the code due to the laborious process of integrating various portions of the code. With a more modular system design, however, debugging code and testing programs can be simplified as we are able to test individual components and more people can participate in programming due to the very fact that it is more modular in nature. The second motivation of studying this new system is that we hope to find a solution to the massive wiring issues that plague not only the Cornell Ranger but also the MWB. Figure 1 and Figure 2 shows the wiring problem that has plagued the two robots.

Figure 1: Wiring Problems of MWB

Figure 2: Wiring Problems of Cornell Ranger

The third motivation is to create an electronic control system that has the capacity to handle the more demanding requirements of future walking robots. Since the process of designing an electronic control system from the ground up is very time consuming, the design of the electronic control system has to allow it to be upgradable.

When a robot is in its design phase, it is usually the case that we do not foresee all the components that are needed to make it walk. As such, when the printed circuit board (PCB) is designed and manufactured, it is rarely self sufficient and additional components almost definitely have to be added onto the existing circuitry. With the addition of components outside of those already on the PCB, it is necessary to connect voltage and ground lines as well as data cables from the microcontroller to the added on component. This results in not only an unsightly nest of wires, but also the uncertainty of having a bad connection whenever something fails to work, instead of knowing that it is a software problem.

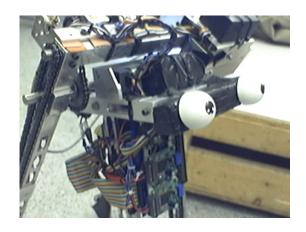

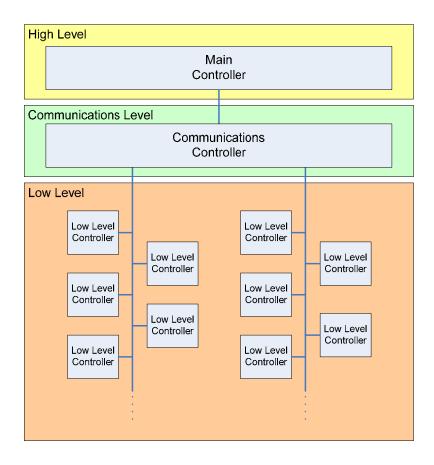

# 1.2. Multiple Microcontroller Electronic Control System

The multiple microcontroller model that is being studied for the next robot proposes using multiple microcontrollers communicating with each other to control various parts of the robot. The model consists of the high level portion, communications level portion and the low level portion. The 3 main portions, as seen in Figure 3, are the High Level portion, the Communications Level portion and the Low Level portion.

Figure 3: Overview of the Proposed Electronic System Architecture

# 1.2.1. High Level Portion

The high level portion consists of the main controller that will be in charge of the controlling the robot on the high level. The code is specific to providing instructions to how the robot should move. Ideally, the code on the main microcontroller is similar to a human-readable list of instructions of how to get a robot to walk. The main controller communicates with the communications controller constantly so as to ensure that the information it has about the robot is up to date.

#### 1.2.2. Communications Level Portion

The main purpose of the communications level is to act as a bridge between the main controller in the High Level and the low level microcontrollers in the Low Level. It is responsible for the data flow between the two other levels. It acts very much like a router, collecting, formatting and redistributing information between all the microcontrollers in the system.

In an actual implementation, the high level portion and the communications level portion may or may not be implemented on different microcontrollers. This would depend on the final choice of communication protocol and microcontroller used.

## 1.2.3. Low Level Portion

In the low level portion, it consists of a number of low-level microcontrollers. Each of these microcontrollers is be responsible for controlling a subset of the sensors and motors based either on function or location. Connected via a network with the communications controller, the multiple low level controllers send information collected via the sensors and receive instructions of what to carry actions to execute, to and from the communications microcontroller.

#### 1.3. Structure of Report

This report would first seek, in the Design Problem section, to familiarize the reader with the design goals and requirements associated with the project and how the design problem is formulated. The following section would then analyze the structure of the multiple microcontroller electronic control system to allow for better understanding ogf the requirements by arriving at a set of performance indicators that the electronic control system should be designed to meet.

The report would then proceed to shortlist suitable microcontroller from those available on the market and compare their capabilities with a list of functionality that the MMECS needs to have. It will also perform an in depth evaluation of 3 previously chosen communication protocols to determine which is the most suitable. Based on the results from the evaluation as well as the shortlisted microcontrollers, the details on the implementation of the system would be decided upon.

This report documents the process of setting up the framework for future work to be performed on setting up the multiple microcontroller electronic control system as well as designing one of the components of the system.

# 2. Design Problem

#### 2.1. Problem Formulation

This Masters of Engineering design project was part of the research team's efforts to design an electronic control system for robots built in the future based on the motivation as described in the section above. This project serves as an initial foray into the development of the MMECS to determine key components in the system. This design process started off in an open-ended manner as a vague idea of the intended system design and layout.

In order to formulate more specific design requirements and specifications for the robot, various members of the research team were consulted to understand the inadequacies of the electronic control system in the current robot. These findings where then matched with the vision of the capabilities for future robots to obtain the design requirements and specifications for this project.

#### 2.2. Design Requirements

In designing the electronic control system for this project, concerns of the software, hardware as well as the physical system developers have to be taken to account. The following core design requirements are key to the usability and success of the electronic control system

- 1. The electronic control system shall be modular

- 2. The electronic control system shall be easily upgradable

- 3. The electronic control system shall be easy to use

- 4. The electronic control system shall have a low power consumption

#### 2.3. Design Goal

The goal of this design project can be divided up to 3 main groups of tasks

- Choosing suitable microcontrollers and components

- Evaluation and testing of various potential suitable communication protocols.

Subsequently choosing the most appropriate configuration.

- Deciding on the physical layout of the electronic control system. If time permits,

the hardware of the system would be designed, built and ready to use.

# 3. Analysis of the Multiple Microcontroller Electronic Control System

To design an electronic control system that would fit the design requirements, it is necessary to analyze the attributes unique to the electronic control system before starting on the design proper. This project performs an analysis of the Multiple

Microcontroller Electronic Control System by studying the possible implementations of the system on a typical walking robot. By hypothesizing possible implementations of the system on the robot, the capacity of the protocols that is needed to support the data flow throughout the system can be calculated.

The model that will be used to analysis the electronic control system will have the following basic assumptions:

- 1.Each Microcontroller will have on average 5 sensors, corresponding to 5 data points

- 2. Each data point would have to be updated once every millisecond. (1000 times a second)

- 3. Each data point is a floating point value (4 bytes)

- 4. Each data point has a corresponding address field which would take up to 4 bytes

Using these assumptions, the number of low-level microcontrollers can be varied to obtain the necessary bandwidth of the communications protocols to support that particular set up. Table 1 below shows the 3 requirements and the bandwidth that is needed.

|                                  | Units                  | Values    |           |           |

|----------------------------------|------------------------|-----------|-----------|-----------|

| # Low-level Microcontroller      | uControllers           | 10 16 2   |           | 20        |

| # Datapoints per Microcontroller | Datapoints/uController | 5         |           |           |

| Update Frequency                 | times/Datapoint/sec    | 1000      |           |           |

| Bits per data point              | bits                   | 64        |           |           |

| Total bits/sec                   | bits per second        | 3,200,000 | 5,120,000 | 6,400,000 |

Table 1: Requirements and the bandwidth that is needed.

# 4. Short-listing Microcontrollers

There is a huge assortment of microcontrollers available in the market today with many designed to suit different industries such as the automotive industry and the portable electronics industry. Based on the requirements of the Multiple Microcontroller Electronic Control System, we are able to shortlist a couple of potential microcontrollers available on the market. This project will take the opportunity to test and use the microcontrollers from the shortlist during the evaluation of protocols.

Due to the need to maintain low power consumption, this project would focus on using ARM microcontrollers. The ARM processor architecture is a 32-bit Reduced Instruction Set Computer (RISC) processor developed by ARM Limited that is used widely in a number of embedded designs. Due to their low power consumption, this processor

architecture is very dominant in the mobile electronics market. Currently, the ARM family of processors accounts for approximately 75% of all embedded 32-bit CPUs, making one of the most widely used computer architectures in the world.

The shortlisted microcontrollers are chosen based on the following few criteria.

- The microcontroller would have the ARM architecture due to the need for low power consumption as mentioned above.

- Compute and compare the estimate of power consumption per unit cycle of the microcontroller core. For this criterion, a simple approach would be finding the hypothetical power consumption if the microcontroller speed is 20MHz.

- Compare the maximum microcontroller speed, to estimate its computing capability

- List support peripherals and functionality

- Vectored Floating Point (VFP) Unit:for fast floating point calculations

o SD Card interface: for information logging purposes

o Direct Memory Access: support for communication protocol

o Serial Peripheral Interface (SPI): support for communication protocol

Universal Serial Bus (USB): support for communication protocol

o Controller Area Network (CAN): support for communication protocol

- Number of Timers

- Number of PWMs

- Number of Analog to Digital Converters (ADC)

The shortlisted microcontrollers are shown in Appendix 1.

# 5. Evaluating Protocols

Choosing the right protocols for use to communicate between the various microcontrollers is important. The suitable protocols would need to not only have the capacity to support the amount of data flow throughout the network, but also have reasonable software overhead so as not to overwhelm the microcontroller that it is on.

This phase of evaluating different protocols for their suitability is aimed at choosing a communications protocol for data transfer between the main microcontroller and communications microcontroller, as well as a communications protocol for data transfer between the communications microcontroller and the various low level microcontrollers. The reason for dividing the protocol selection to two different parts is to allow for flexibility. There is, however, a possibility that a single communications protocol is suitable to handle the data flow between the main microcontroller and the various low level microcontrollers.

It is also important to keep in mind that it is subject to the availability of the protocols on viable microcontrollers. A particular protocol can potentially be evaluated to be optimal, but if it were not implementable on a viable microcontroller, it would be

unsuitable for this project.

In evaluating the protocols, microcontrollers together with the necessary components would be used to build a test set up. The IAR Embedded Workbench KickStart Edition from IAR systems is used to program the microcontrollers.

The evaluation process would comprise the following 3 communications protocol

- 1. Controller Area Network (CAN-bus)

- 2. Universal Serial Bus (USB)

- 3. Serial Peripheral Interface (SPI) with Direct Memory Access (DMA)

# 5.1. Controller Area Network (CAN-Bus)

## <u>5.1.1. Overview</u>

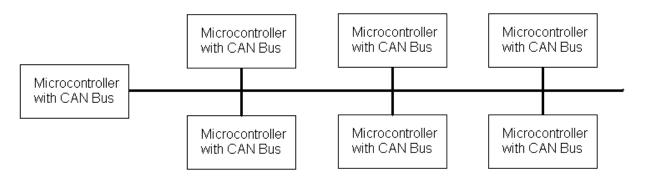

CAN-Bus is a computer network protocol and a bus standard designed for devices to communicate within the network without the need of a host computer. Intel Corporation and Bosch jointly developed CAN-Bus in 1988 and it was specifically targeted for automotive applications. Figure 4 shown below illustrates a high level view of a typical CAN-Bus network.

Figure 4: High Level View of a Typical CAN-Bus network

The CAN-Bus protocol has the following characteristics

- Bit rates up to 1 Mbit/s are possible at network lengths below 40 m.

Decreasing the bit rate allows longer network distances. (See Table 2)

- An automatic 'arbitration free' transmission. A CAN message that is transmitted with highest priority will 'win' the arbitration, and the node transmitting the lower priority message will sense this and back off and wait.

- 3. A multi-master hierarchy, which allows building intelligent and redundant system. If one network node is defect, the network is still able to operate.

- 4. Broadcast communication. A sender of information transmits to all devices on the bus. All receiving devices read the message and then decide if it is relevant to them. This guarantees data integrity as all devices in the system use the same information. Each node is able to send and receive messages, but not simultaneously. A message consists primarily of an ID and up to messages 8 bytes long.

- 5. Sophisticated error detecting mechanisms and re-transmission of faulty

messages. This also guarantees data integrity.

6. Each CAN message can carry from 0 to 8 bytes of data

| Bit Rate   | Bus Length |

|------------|------------|

| 1MBit/s    | 30 m       |

| 800 kBit/s | 50 m       |

| 500 kBit/s | 100 m      |

| 250 kBit/s | 250 m      |

| 125 kBit/s | 500 m      |

| 50 kBit/s  | 1000 m     |

| 20 kBit/s  | 2500 m     |

| 10 kBit/s  | 5000 m     |

Table 2: CAN-Bus Maximum Bit Rate vs. Bus Length

Although the CAN bus standard specifies that the maximum bit rate is 1Mbit per second, there are CAN bus transceivers available on the market which support up to 2Mbit per second. To be able to use them, however, the bus length has to be significantly shorter then 30m.

## 5.1.2. Potential

It is easy to see that the potential use of this communications protocol would be in facilitating the data flow between the communications microcontroller and the low level microcontroller. As the protocol is that of broadcast communication, every microcontroller in the CAN-Bus network would be able to listen in on what is being

transmitted. This can be crucial as the communications microcontroller would only need to send information meant for multiple low level microcontrollers only once, rather than sending the same data multiple times, wasting bandwidth.

# 5.1.3. Experimental Setup and Testing

For evaluating the CAN-Bus protocol, the evaluation board for MAC7111 microcontroller was used. Figure X shows the picture of the MAC7111 evaluation board. The MAC7111 microcontroller is from Freescale and it was chosen as it is an ARM7 with relatively low power consumption and it had 4 CAN-Bus ports.

Figure 5: MAC7111 Low Cost Evaluation Board

To test the CAN-Bus protocol, 2 of the CAN-Bus ports were wired together and data was sent through one port and received on the other. The received data was checked against the data sent to check for errors. The speed of the data transmission and the

length of the CAN-bus were varied to obtain the throughput of the CAN-Bus under various conditions.

It is important to note that similar to the evaluation of the USB protocol, since the test is performed on a single microcontroller, the rate at which the data is transferred is not merely the total data transferred over the total time taken. This is the result of the microcontroller having to constantly send data to one CAN port and receive data from the other CAN port. To get a better approximation of the data rate, timers and interrupts were used to measure the time used to receive the data on the host side. Using this approach, a close approximation to the actual data rate can be obtained.

In addition, the experiment also attempted to over clock the CAN-bus to see if it could handle data transmission speeds of up to 2Mbits/sec without any significant drop in throughput due to errors in transmission.

For the perimeters of the experiment, two CAN ports would communicate with each other - one sending data and the other receiving data. The CAN Bus would be set at 500kbps, 750kbps, 1000kbps, 1500kbps and 2000kbps, with the data rate calculated as total bits received over the time taken to receive the data on one CAN port. The CAN Bus would have it length varied from 100cm to 300cm.

Appendix 2 contains the full listing of the code.

## 5.1.4. Results

Running the above-mentioned experiment for different bus lengths at different speed for 30 times each, the averages of the data rates (in kilobits per second) are obtained. Table 3 below shows the summary of the results obtained. Appendix 3 contains the full results of the experiment.

| CAN Bus Speed | Length of Bus |         |         |

|---------------|---------------|---------|---------|

| (kbps)        | 100cm         | 150cm   | 300cm   |

| 500           | 361.29        | 362.19  | 361.37  |

| 750           | 535.34        | 535.76  | 535.37  |

| 1000          | 696.90        | 697.33  | 697.53  |

| 1500          | 1021.59       | 1009.09 | 997.30  |

| 2000          | 1297.51       | 1281.98 | 1265.30 |

Table 3: Results of CAN Bus Experiment (data rates in kbps)

#### 5.2. Universal Serial Bus (USB)

# 5.2.1. Overview

The Universal Serial Bus (USB) is a widely used protocol, not only in personal computers, but also in various different electronic gadgets. USB was designed to allow many peripherals to be connected using a single standardized interface socket and to improve the plug-and-play capabilities by allowing devices to be connected and disconnected. The USB protocol has the following key features:

- 1. USB is a protocol that operates with a single host with multiple peripherals.

- 2. Up to 127 devices can connect to the host, either directly or by way of USB hubs.

- 3. Individual USB cables can run as long as 5 meters and with hubs, devices can be up to 30 meters away from the host.

- 4. A USB cable has two wires for power and a twisted pair of wires to carry the data.

- 5. USB devices are hot-swappable.

- 6.The USB protocol is a widely supported with drivers available for most operating systems.

In the analysis of the USB protocol, this part of the project will look at the implementation of a full speed USB protocol.

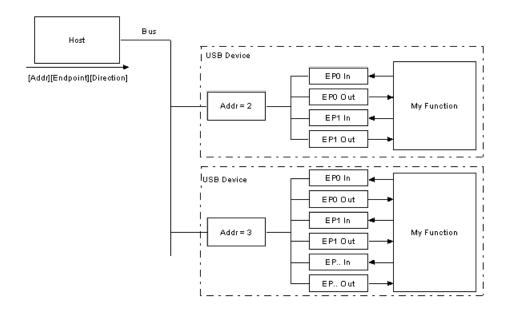

The USB protocol is based on a system of endpoints that are established between the host and the device during enumeration, with a maximum of 16 endpoints between the host and each device. These endpoints can be viewed as "pipes" of data flow between the host and the device. Figure 6 below illustrates the concept of endpoints in USB.

Figure 6: Concept of Endpoints in USB

The USB full-speed protocol supports 3 different schemes for data transfers—Interrupt transfers, Bulk transfers and Isochronous transfers. For interrupt transfers, the maximum data rate is low as only 1 packet of information can be transferred at a time. As the name suggests, interrupt transfers only occur when the data is received on the USB buffer and an interrupt is asserted. As each USB frame is 1 millisecond in duration, the interrupt that gets asserted is only be serviced once every millisecond. Since the maximum size of a USB packet is 64 bytes, this implies that the maximum data rate of the USB interrupt driven transfer is 512kbps. For Bulk transfers, the data rate is the highest among the three schemes as it allows for multiple packets to be sent at a single time. The USB protocol is capable of supporting up to 19 packets of 64 bytes for a bulk transfer, allowing it to reach up to speeds close to the maximum of 12Mbps. For Isochronus transfers, the data rate is unreliable as this scheme is meant for data streaming. It utilizes the remaining unused bandwidth to transfer data between the

host and the device. Given the above 3 schemes and time considerations, the analysis would only be performed using the bulk transfers where the data rate is high.

#### 5.2.2. Potential

There are 2 features of the USB protocol that makes it attractive as a protocol that this project would use. Firstly, the data rate of the full speed USB is 12Mbps and it is definitely high enough for the purposes of this project. Comparing with the analysis of the MMECS model as discussed in the earlier section, the data rate more than satisfies the needs of the model and it even provides capacity for further expansion. The second feature is that the USB protocol is a widely supported protocol with drivers easily available for most operating systems. This means that having a USB connection would allow us to easily connect the robot up to a PC where testing and the development of the robot itself would be greatly facilitated.

# 5.2.3. Experimental Setup and Testing

After some initial product and protocol research, the USB protocol is found to be rather challenging to implement. Having to implement the whole USB state machine, together with the error checking and timing issues would potentially occupy a significant amount of time and set this project back for a considerable amount of time. In addition, a

significant number of the short listed microcontrollers as listed earlier in the report lack USB functionality.

Given this situation, it was decided to perform the evaluation of the USB protocol using an external USB controller that communicates with the microcontroller via the Serial Peripheral Interface (SPI). This would be beneficial to the project as it would act as a stepping stone to having a better understanding of USB as the USB controller takes care of some of the lower level functions. Additionally, the interface between the microcontroller and the USB controller is one that is rather easy to use.

The SPI-USB Controller that will be used for the evaluation of the USB protocol is the MAX3421E from Maxim. The MAX3421E is a SPI-USB controller capable of Full Speed USB transmissions. For testing purposes, the development board for the MAX3421E as well as the MCB2130 development board from Keil was used. The MCB2130 development board contains the LPC2138 microcontroller from NXP, while the development board for the MAX3421E comes with both the MAX3421E and MAX3420E (MAX3420E is the peripheral device version of the MAX3421E).

The approach to testing the USB protocol using the above-mentioned components is to send data out through the peripheral side of the USB connection and receive data from the host side of the connection.

It is important to note that since the test is performed on a single microcontroller, the rate at which the data is transferred is not merely the total data transferred over the

to the USB device (MAX3420E) and receive data from the USB host (MAX3421E). To get a better approximation of the data rate, timers and interrupts were used to measure the time used to receive the data on the host side. Using this approach, the data rate on the full speed USB connection can be measured.

Maxim provided an example base code to demonstrate the use of the development board that they manufactured. The example code provided was originally for Keil MicroVision software. The example code simulated the USB device as a Human Interface Device (HID). The example code provide by Maxim can be found at Maxim's website

The code was ported over for use on IAR Embedded Workbench and modified for use to evaluate the USB protocol. All changes to the example code, for ease of documentation purposes, were kept to the main code file – lpc2138.c, which can be found in Appendix 4.

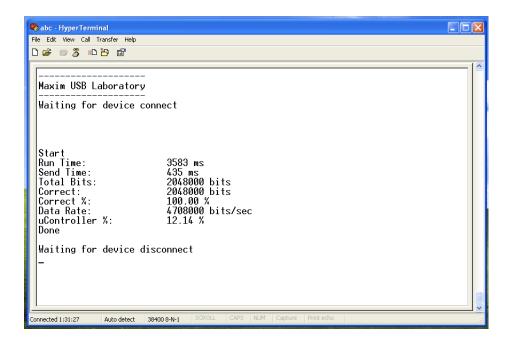

#### 5.2.4. Results

The data rate was measured for the bulk transfers over full speed USB. Table 4 contains the parameters used to determine the data rate that can be achieved using the MAX3241E.

| Packet Length                   | 64 bytes           |  |

|---------------------------------|--------------------|--|

| # of Packets per Bulk Transfer  | 16 packets         |  |

| # of Bulk Transfer per Run      | 250 bulk transfers |  |

| Total bytes transferred per Run | 256000 bytes       |  |

Table 4: Parameters used in experiment

A total of 50 runs were carried out to determine the data rate. The table of the results can be found in Appendix 5. Figure 7 below shows a screenshot of one of the runs where the result was parsed via UART to hyperterminal.

Figure 7: Screen Capture of a USB data typical rate test

Table 5 contains the summary of the results of the data rate for bulk transfers using full speed USB.

|         | Data Rate (bps) | % Correct | uController Load |

|---------|-----------------|-----------|------------------|

| Average | 4723920         | 100.00    | 12.54            |

| Std Dev | 147139          | 0.00      | 0.07             |

Table 5: Summary of Results for full speed USB bulk transfers

## 5.3 Serial Peripheral Interface (SPI) with Direct Memory Access (DMA)

## 5.3.1a. Overview - SPI

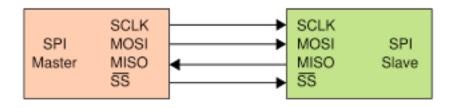

The Serial Peripheral Interface Bus or SPI bus is a synchronous serial data link standard that operates in full duplex mode. This communications protocol consists of 4 wires – Clock, Master In Slave Out (MISO) and Master Out Slave In (MOSI). Devices communicate in a master/slave mode, allowing for multiple slaves with individual "Slave Select" lines. Figure 8 below shows an example of a SPI bus with a single Master and a single Slave.

Figure 8: SPI bus with a single Master and a single Slave

The SPI protocol is a very common protocol and it can be considered as a standard feature in a wide range of microcontrollers. The maximum speeds of the SPI bus usually very between microcontrollers. The maximum speed is usually a factor of the CPU speed of the SPI master microcontroller. For example, if a microcontroller has a CPU speed of 60Mhz, the possible SPI would be 60Mhz divided by a range of user definable values. Hence, it is possible to have a fast SPI speed if a microcontroller with a fast CPU speed is used.

#### 5.3.1b. Overview - DMA

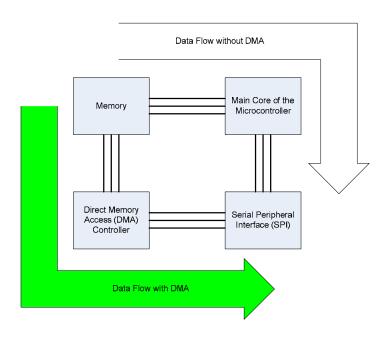

Direct memory access (DMA) is a feature that allows certain hardware subsystems within the computer to access system memory for reading and writing independently of the main core of the processor. DMA channels have the ability to transfer data to and from devices with much less overhead than microcontrollers without a DMA channel.

Without DMA, the main core of the processor typically has to be occupied for the entire time it's performing a transfer, while with DMA, the main core initiates the transfer, do other operations while the transfer is in progress, and receive an interrupt from the DMA controller once the operation has been done.

Figure 9 below shows the differences between data transfers that use DMA and those that do not, for data that resides in Memory to the Serial Peripheral Interface (SPI). For the purposes of this project, the data transfer between the main controller and the

communications controller will be using the Serial Peripheral Interface (SPI) protocol and it will utilize DMA and implemented on the two respective controllers.

Figure 9: Differences in Data Transfers for SPI using DMA and not using DMA

## 5.3.2. Potential

The SPI with DMA implementation is especially useful for our purposes as it reduces the load on the core of the main controller and free up more resources for the needs of the robot. On the high level programming level, it would be straightforward as the process to manage the dataflow would be setting the appropriate bits in the microcontroller to get the Direct Memory Access re-started once every update interval. This also has an additional benefit as it would reduce the processing load on the main microcontroller,

freeing up precious computing power.

## 5.3.3. Experimental Setup and Testing

The testing of SPI with DMA is carried out between the LPC3180 and the LPC2368, both from NXP. The LPC3180 is an ARM9 microcontroller while the LPC2368 is an ARM7 microcontroller, both of which have Serial Peripheral Interface and are capable of performing Direct Memory Access.

The reasons for using these 2 microcontrollers are two fold. Firstly, these two microcontrollers as mentioned in the previous section, the ARM9 microcontrollers are a class of more powerful microcontrollers as compared to ARM7 microcontrollers, using the LPC3180 would allow us to gain experience in programming and working with ARM9 microcontrollers. Secondly, using an ARM9 microcontroller as the SPI master and the ARM7 microcontroller as the SPI slave closely parallels the potential use of this communications protocol in the Multiple Microcontroller Electronic Control System. By using a similar set up, possible problems or flaws that is currently unforeseen with the set up can be uncovered.

The LPC3180 operates at a maximum of 208MHz and has a SPI capable of up to 52MHz, while the LPC2368 operates at a maximum of ??MHz and has a SPI capable of up to ??MHz. To allow for a SPI speed that is implementable on both the microcontrollers, the SPI for this analysis would be initially set at 8MHz.

The code for setting up the analysis on the LPC3180 and LPC2368 is found on Appendix 6 and 7 respectively.

# 5.3.4. Results

The code written for both the microcontrollers did not seem to be able to transfer data consistently and reliably over the SPI using DMA using the parameters as described above. Though data was transferred, only the first few bytes that are received are consistent with the data sent.

In an attempt to understand the problem, the code was run to transfer 10 bytes of data over the SPI using DMA with LPC3180 being the SPI master. For the ease of illustration and explanation of the problem, ASCII characters were sent. Table 6 shows the outcome of the failed data transfer attempt from LPC2368 to LPC3180 and Table 7 shows the outcome in the reverse direction.

| Byte | Byte<br>Sent | Byte<br>Received |

|------|--------------|------------------|

| 1    | Α            | Α                |

| 2    | В            | В                |

| 3    | С            | С                |

| 4    | D            | D                |

| 5    | Е            | 0                |

| 6    | F            | 0                |

| 7    | G            | 0                |

| 8    | Н            | 0                |

| 9    | I            | 0                |

| 10   | J            | 0                |

Table 6: Outcome of failed data transfer from LPC2368 to LPC3180

| Byte | Byte<br>Sent | Byte<br>Received |

|------|--------------|------------------|

| 1    | Α            | Α                |

| 2    | В            | В                |

| 3    | С            | С                |

| 4    | D            | D                |

| 5    | Е            | 0                |

| 6    | F            | 0                |

| 7    | G            | 0                |

| 8    | Н            | 0                |

| 9    | Ī            | 0                |

| 10   | J            | 0                |

Table 7: Outcome of failed data transfer from LPC3180 to LPC2368

Looking at the result of the failed data transfer, it can be suspected that the SPI on one of the microcontrollers is unable to keep up with the data transfer. As a result, either the SPI buffers overflows or underflows, resulting in only the first 4 bytes being

successfully transmitted.

This issue was further investigated and it was found that the SPI and the DMA on the LPC2368 was unable to keep up with the SPI speed of 8MHz. The same run was carried out with the SPI at 2MHz and the data was successfully transferred.

Help was sought from the technical support from NXP to confirm the observations and it was confirmed that the Direct Memory Access (DMA) controller was unable to keep up the data transfers between the SPI buffers and the memory locations. The technical support cited 2 explanations for the observations:

- The LPC3180 is designed to run at a significantly higher CPU speed as compared to the LPC3368. Hence, the DMA controller in the LPC3180 is able to keep up with the data transfers, but not the LPC2368.

- 2. The SPI buffer in the LPC2368 is of length 2, while the SPI buffer in the LPC3180 is of length 56. Hence, the SPI buffer in the LPC3180 is able to store more data before the SPI overflows. This is especially so since the SPI is operating at a high speed.

Since most of the other ARM7 microcontrollers are similar in terms of computing power as compared to the LPC2368, it is unlikely that the problem would be nonexistent if we replace the LPC2368 with another ARM7 microcontroller. As a result, using SPI with DMA is only possible within the constraints of this project to have a transfer speed

within the ballpark of about 2MHz.

# 6. Choosing Microcontrollers and Protocols

After short-listing the microcontrollers and evaluating the communications protocols, an informed decision can be made with regards to choosing the appropriate microcontroller and communication protocol.

For the communication protocols, the analysis revealed that using SPI with DMA does not seem to be a viable option due to the inability of the DMA controller to keep up with the speed of the data transmission.

The CAN Bus protocol seemed rather promising as the experiments showed that speeds of up to 2000kbps were possible. Though the actual rate is slower due to the protocol overhead, the extra bandwidth obtained by "overclocking" the CAN Bus would definitely go a long way. Although the CAN Bus is comparatively slower in speeds as compared to the other protocols analyzed, it is possible for the system to have multiple CAN Buses in parallel to effectively have a higher data rate. This is possible as many microcontrollers, as seen from the shortlist, have multiple CAN ports. It is important, however, to note that the more powerful microcontrollers tend not to have CAN ports on them. As we can see from the shortlist, the LPC3180 and i.MX31 microcontrollers do not have CAN ports, but they are seemingly very attractive main microcontrollers for the project.

The full speed USB protocol that was analyzed is also very promising. From the results, the analysis showed that it had sufficient bandwidth and it is possible for it to be implemented using external controllers that interface with a host microcontroller via SPI. Compared to the CAN bus, it would be almost equivalent in terms of data rate if 4 CAN Buses were used in parallel. One downside to the USB protocol is the implementation of the USB stack as well as its state machine. Just looking at the code used to setup the data transfers between the host and device, it is clear that the computational power needed to run the USB protocol is sizable. In addition, due to the complex nature of the USB protocol, it might not be suitable to proceed with implementing a full scale USB protocol along with the device drivers given the manpower and capability of the research lab at the current point of time. Hence, USB might only suitable for implementation on a smaller scale where it is possible to temporarily ignore some of the USB specifications.

Given the above analysis and results, the best implementation of the multiple microcontroller electrical control system would be for the USB protocol to be used between the main microcontroller and the communications controller and the CAN Bus protocol over 4 separate but parallel networks would be used for communication between the communications controller and the multiple low level controllers. The communications controller would effectively act as a router to transmit data not only between the low level microcontrollers and the main controller, but also between the low level microcontrollers if the communicating low level microcontrollers are on

separate CAN Bus networks. As for the microcontrollers themselves, the following would be the microcontrollers for the electronic control system.

• Main Microcontroller: i.MX31 from Freescale

Communications Microcontroller: LPC2194/01 from NXP

Low level Microcontroller: LPC2194/01 from NXP

In my opinion, this would be the most suitable implementation as it combines the strengths of both the CAN Bus and USB protocols. Furthermore, the task of implementing of the actual system would not be too overwhelming for the future student researchers to continue work on.

One key reason for deciding on this implementation for the electronic control system is also scalable. If there would be a future need to increase the capacity of the data transmission between the microcontrollers, this implementation would easily allow for an upgrade. Firstly, the i.MX31 supports both full speed USB as well as hi speed USB, if the capacity for the full speed USB eventually becomes insufficient, a switch can be made to the hi speed USB. By adding a hi-speed USB hub, the communications microcontroller can be replicated to obtain multiple CAN Bus networks to support the bandwidth as well. Although, the implementation of the USB protocol to communicate from a singe host to multiple devices is not simple or trivial, there would be more time between currently and the future for the USB protocol to be fully implemented.

# 7. Initial progress on building the MMECS

#### 7.1. Setting Up Initial Base Code

As the microcontroller and the communication protocols have been chosen for the whole system, the actual building of the system and programming of the microcontrollers to support the communications protocols and their respective tasks would natural follow in the design process. However, as mentioned in the introduction that the scope of this project does not encompass the entirety of the process till the network-based electronic communication system as ready as a "product" for use in the development of a robot, other students researchers would have to continue on where this project left off.

In programming a microcontroller, especially if it is an unfamiliar microcontroller or a new programming environment, there is always the initial set up of the project files, linker files as well as other settings. This can possibly be a steep learning curve. Hence, if students were provided with a sample project with straightforward no-frills code, they would not have to worry about getting the settings correct and understanding the sample code. The students would be able to begin the programming task almost immediately, saving effort and time.

The initial base code written consists of very basic elements to get a typical student programmer started as soon as possible. The code accomplishes the following:

Initialize the Phase Lock Loop in the microcontroller so the user can easily change

the CPU speeds by changing variables

Initialize the Vectored Interrupt Controller in the code to handle interrupts

• Initialize a timer and its interrupt. This acts more as an example to initialize

interrupts on the microcontroller.

• Toggle an output. This acts more as a visual cue to the user so that they would

know that the microcontroller is running the code.

Instructions on how to change key settings in the project files are also included as

comments in the code. The full listing of the example code can be found in Appendix 8.

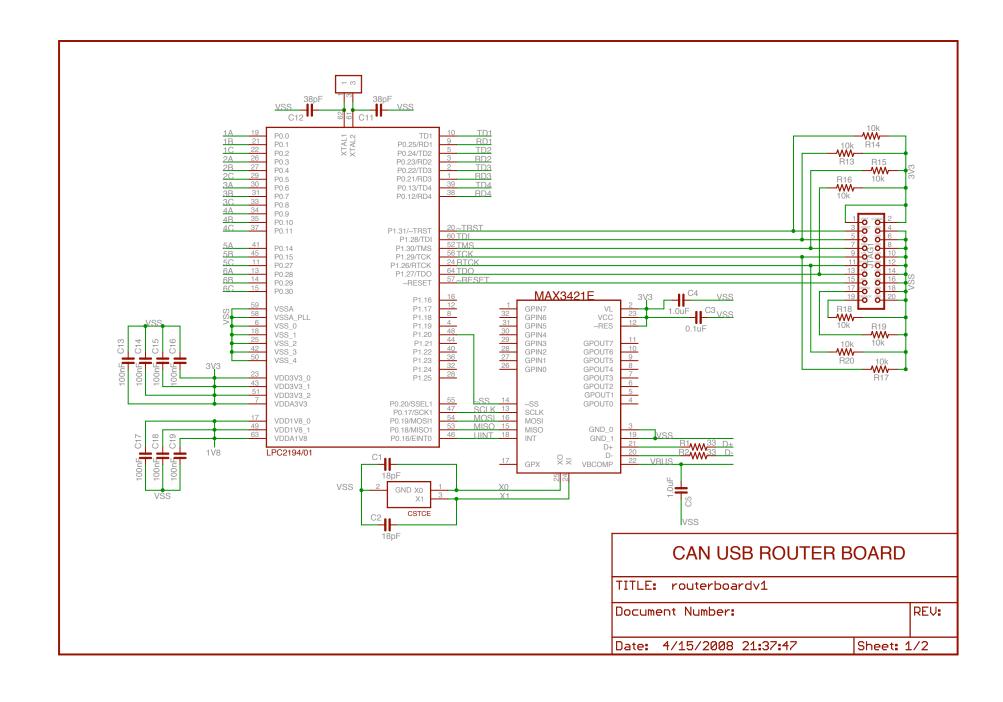

7.1. Designing the Communications microcontroller

Based on the recommendations mentioned in the previous section, the communications

controller would essentially be a LPC2194/01 microcontroller that receives and

transmits data over USB and CAN Bus protocols. A printed circuit board (PCB) would be

designed to house the necessary components and circuits to function as a bridge

between the main microcontroller and the low level microcontrollers.

The following are the rough list key of parts needed for the design on the

communications circuit board:

• LPC2194/01

-microcontroller

MAX3421E

-SPI to USB controller

CAN transceivers

-to use the CAN bus protocol

• JTAG connection -for programming

• LEDS -as visual indicators

• Switching Power Regulators -to step down the power for use on the board

The schematic for the design of the communications circuit board is attached as Appendix 9. However, as some of the actual components are currently still being tested by other members of the trace layout of the communications board is placed on hold until all testing of components are complete.

#### 7. Conclusion

After performing the analysis of the MMECS, shortlisting microcontrollers, as well as the evaluation of the various communications protocols, this project arrived at a recommendation for the MMECS. The recommendation is a follows

#### Microcontrollers

o Main Microcontroller: i.MX31 from Freescale

o Communications Microcontroller: LPC2194/01 from NXP

Low Level Microcontroller: LPC2194/01 from NXP

#### • Communication Protocols

Main and Communications Microcontroller: Full Speed USB

Communications and Low Level Microcontroller: CAN Bus

The recommendation takes into account not only the technical requirements of the project, but it also considers the number of personnel and expertise so that the multiple microcontroller electronic control system can be reasonably completed in time for use in the next walking robot built. In addition, the nature of the design also allows for upgradability for incremental changes to be made to the electronic control system over time.

Some initial work has also been done in building the MMECS. The initial base code was written to allow for more individuals to participate in building of the MMECS and the schematic of the communications microcontroller is also done.

# References

Original CAN Specification <a href="http://www.can.bosch.com/docu/can2spec.pdf">http://www.can.bosch.com/docu/can2spec.pdf</a>

CAN Official Website <a href="http://www.canbus.us/">http://www.canbus.us/</a>

USB Official Website <a href="http://www.usb.org">http://www.usb.org</a>

Freescale Company Website <a href="http://www.freescale.com">http://www.freescale.com</a>

NXP Company Website <a href="http://www.nxp.com">http://www.nxp.com</a>

Keil Company Website <a href="http://www.keil.com">http://www.keil.com</a>

IAR Systems Company Website <a href="http://www.iar.com">http://www.iar.com</a>

IAR Emdedded Kickstart User Guide <a href="ftp://ftp.iar.se/WWWfiles/arm/Guides/ouarm">ftp://ftp.iar.se/WWWfiles/arm/Guides/ouarm</a> 13.pdf

LPC2000 Discussion Forum <a href="http://www.embeddedrelated.com/groups/lpc2000/1.php">http://www.embeddedrelated.com/groups/lpc2000/1.php</a>

| uController | Chip<br>Maker | Chip<br>Type | Package      | Max<br>CPU<br>speed<br>(MHZ) | Pwr Est.<br>(20MHz) | VFP | SD<br>Card | DMA | Timer | USB<br>Host  | USB<br>OTG | CAN | SPI<br>or<br>SSP | PWM | ADC        | Other                |

|-------------|---------------|--------------|--------------|------------------------------|---------------------|-----|------------|-----|-------|--------------|------------|-----|------------------|-----|------------|----------------------|

| i.MX31      | Freescale     | ARM11        | BGA 457      | 532                          | 10mA                | Yes | Yes        | Yes | 3     | 2xFS<br>1xHS | 1          | -   | 3                | 1   | -          |                      |

| LPC3180     | NXP           | ARM9         | BGA 320      | 208                          | 20mA                | Yes | Yes        | Yes | 2     | 1xFS         | 1          | -   | 2                | 2   | -          |                      |

| AT91SAM7A3  | Atmel         | ARM7         | LQFP<br>100  | 70                           | 50mW                | No  | No         | Yes | 2     | -            | -          | 2   | 4                | 9   | 16(10bit)  |                      |

| LPC2368     | NXP           | ARM7         | LQFP<br>100  | 72                           | 115mW               | No  | Yes        | Yes | 6     | 1xFS         | -          | 2   | 3                | 6   | 6 (10 bit) |                      |

| LPC2129     | NXP           | ARM7         | LQFP<br>64   | 60                           | 35mW                | No  | No         | No  | 2     | -            | -          | 2   | 2                | 6   | 4 (10 bit) | SPI/SSP<br>7.5Mbit/s |

| LPC2129/01  | NXP           | ARM7         | LQFP<br>64   | 60                           | 35mW                | No  | No         | No  | 2     | -            | -          | 2   | 2                | 6   | 4 (10 bit) | SPI/SSP<br>30Mbit/s  |

| LPC2194     | NXP           | ARM7         | LQFP<br>64   | 60                           | 35mW                | No  | No         | No  | 2     | -            | -          | 4   | 2                | 6   | 4 (10 bit) | SPI/SSP<br>7.5Mbit/s |

| LPC2194/01  | NXP           | ARM7         | LQFP<br>64   | 60                           | 35mW                | No  | No         | No  | 2     | -            | -          | 4   | 2                | 6   | 4 (10 bit) | SPI/SSP<br>30Mbit/s  |

| MAC7141     | Freescale     | ARM7         | LQFP-<br>100 | 80                           | 250mW               | No  | No         | Yes | 10    | -            | -          | 2   | 2                | 16  | -          |                      |

| STR75xF     | STMicro       | ARM7         | BGA<br>64    | 60                           | 100mW               | No  | No         | Yes | 3     | 1xFS         | -          | 1   | 2                | 3   | 16(10bit)  |                      |

| STR73xF     | STMicro       | ARM7         | BGA<br>64    | 60                           | 430mW               | No  | No         | Yes | 6     | -            | -          | 3   | 2                | 6   | 16(10bit)  |                      |

| STR71xF     | STMicro       | ARM7         | BGA<br>64    | 32                           | 160mW               | No  | No         | No  | 4     | 1xFS         | -          | 1   | 2                | 6   | 8 (12 bit) |                      |

| STR91xF     | STMicro       | ARM9         | BGA-65       | 96                           | 130mW               | No  | No         | Yes | 10    | 1xFS         | -          | 1   | 2                | 6   | 8 (10 bit) |                      |

```

#include "MAC7100InterruptHandler.h"

#include <iomac7100.h>

#include <intrinsics.h>

** usefull for bitmask operations

#define BIT0 ( 0x0000001 )

#define BIT1 ( 0x00000002 )

#define BIT2 ( 0x0000004 )

#define BIT3 ( 0x00000008 )

#define BIT4 ( 0x00000010 )

#define BIT5 ( 0x00000020 )

#define BIT6 ( 0x00000040 )

#define BIT7 ( 0x00000080 )

#define BIT8 ( 0x00000100 )

#define BIT9 ( 0x00000200 )

#define BIT10 ( 0x00000400 )

#define BIT11 ( 0x00000800 )

#define BIT12 ( 0x00001000 )

#define BIT13 ( 0x00002000 )

#define BIT14 ( 0x00004000 )

#define BIT15 ( 0x00008000 )

#define BIT16 ( 0x00010000 )

#define BIT17 ( 0x00020000 )

#define BIT18 ( 0x00040000 )

#define BIT19 ( 0x00080000 )

#define BIT20 ( 0x00100000 )

#define BIT21 ( 0x00200000 )

#define BIT22 ( 0x00400000 )

#define BIT23 ( 0x00800000 )

#define BIT24 ( 0x01000000 )

#define BIT25 ( 0x02000000 )

#define BIT26 ( 0x04000000 )

#define BIT27 ( 0x08000000 )

#define BIT28 ( 0x10000000 )

#define BIT29 ( 0x20000000 )

#define BIT30 ( 0x40000000 )

#define BIT31 ( 0x80000000 )

#define LED MASK ( 0xFFUL<<8 )</pre>

void init clock(void);

void INTC CANA Handler (void);

void INTC_CANB_Handler (void);

void INTC_PIT1_Handler( void ) ;

void init_flexcanA(void);

void init_flexcanB(void);

unsigned char ledstat=1,a,b,c,d=0,a1,a2,a3,a4,a5,a6,a7,a8;

unsigned long e=0,f=0,t=0;

unsigned char rx[1000];

unsigned char* ptr;

```

```

int main( void )

init clock();

init_flexcanA();

init flexcanB();

/* start/prepare timer */

PITCTRL &= ~( BIT24 ) ; /* enable pit */

PITINTSEL |= ( BIT1 ) ; /* timers generate interrupts */

PITINTEN |= ( BIT1 ) ; /* enable timer interrupts */

MAC7100InstallIRQ( INTC PIT1, 0, INTC PIT1 Handler );

/* set PF.8-15 as output */

CONFIG8 F = CONFIG9 F = CONFIG10 F = CONFIG11 F = ( BIT6 ) ;

CONFIG12_F = CONFIG13_F CONFIG14_F = CONFIG15_F = ( BIT6 ) ;

/* enable global interrupts */

ICONFIG \mid = ( BIT4 ) ; /* no fig */

enable interrupt();

/* set the timeout compare interrupt in ms */

TLVAL1 = 2000000; /* set timeout */

PITFLG |= (BIT1); /* clear flag */

PITEN |= (BIT1); /* enable pit1 */

PINDATA12 F=PINDATA13 F=PINDATA14 F=PINDATA15 F=1;

MB0B W0 bit.CODE = 0;

MB0BW1 bit.ID = 0;

MB0B_W0_bit.CODE = 4;

MBOA_W1_bit.ID

= 0;

MB0A_W2_bit.DATA0 = d;

MB0A_W2_bit.DATA1 = 0;

MB0A_W2_bit.DATA2 = d;

MB0AW2 bit.DATA3 = 0;

MB0AW3 bit.DATA4 = d;

MB0A W3 bit.DATA5 = 0;

MB0AW3 bit.DATA6 = d;

MB0AW3 bit.DATA7 = 0;

MBOA WO bit.LENGTH= 8;

MB0A_W0_bit.CODE = 0xC;

while (1) //while loop to blink led

int i=0;

for(i=0;i<100000;i++);

PINDATA12 F bit.DATA = ~PINDATA12 F bit.DATA;

}

```

```

void init_clock(void){

/* Set PLL multiplication factor */

SYNR = 4;

//40Mhz

REFDV = 1;

/* Configure PLL */

PLLCTL_bit.CME = 1;

PLLCTL_bit.PLLON = 1;

PLLCTL bit.AUTO = 1;

PLLCTL_bit.ACQ = 1;

PLLCTL_bit.SCME = 1;

/* Wait for PLL to achieve lock */

while ( (CRGFLG & 0 \times 08) == 0);

/* Switch system clocks over to PLL */

CLKSEL bit.PLLSEL = 1;

/* Configure interrupts */

CRGINT = 0;

/* Configure BDM control register */

BDMCTL = 0;

}

void init flexcanA(void){

//Set Pins G4 and G5 as Peripheral Pins

CONFIG4 G bit.MODE = 1;

CONFIG5 G bit.MODE = 1;

//Set Control Register

= 0;

CTRLA

CTRLA bit.RJW

= 3;

CTRLA_bit.Row

CTRLA_bit.PSEG1 = 2;//

CMDIA_bit.PSEG2 = 2;//

CTRLA bit.PROPSEG = 2;//

CTRLA_bit.TSYN = 1;

CTRLA bit.PRESDIV = 0;

CTRLA bit.LBUF = 0;

CTRLA bit.CLK SRC = 1;

//CTRLA bit.LPB = 1; //Enable Loop back Mod

//Initialize All Message Buffers - in Use

MBOA WO bit.CODE =8;

MB0AW0 bit.IDE =0;

//Initialize All Message Buffers - 1-31 Not in Use

//Initialize All Message Buffers - 1-31 Not in Use MB1A_W0 = 0; MB2A_W0 = 0; MB3A_W0 = 0; MB4A_W0 = 0; MB5A_W0 = 0; MB6A_W0 = 0; MB7A_W0 = 0; MB10A_W0 = 0; MB11A_W0 = 0; MB13A_W0 = 0; MB13A_W0 = 0; MB14A_W0 = 0; MB15A_W0 = 0; MB16A_W0 = 0; MB16A_W0 = 0; MB17A_W0 = 0; MB18A_W0 = 0; MB19A_W0 = 0; MB20A_W0 = 0; MB21A_W0 = 0; MB23A_W0 = 0; MB25A_W0 = 0; MB26A_W0 = 0; MB27A_W0 = 0; MB28A_W0 = 0; MB29A_W0 = 0; MB30A_W0 = 0; MB30A_W0 = 0; MB31A_W0 = 0; MB29A_W0 = 0; MB30A_W0 = 0; MB30A_W0 = 0; MB31A_W0 = 0; MB29A_W0 = 0; MB30A_W0 = 0; MB30A_W0 = 0; MB31A_W0 = 0; MB30A_W0 = 0; MB31A_W0 = 0; MB30A_W0 = 0; MB31A_W0 = 0; MB30A_W0 = 0; MB30A_W0 = 0; MB31A_W0 = 0; MB30A_W0 = 0;

MB31AW0 = 0;

```

```

//Acceptance Mask Bit

RXGMASKA bit.MI = 0;//all 0 in the mask (dont care)

//Interupt Set up

IMASKA = 0 \times 000000000; //Interupt Mask for MB0

IFLAGA = Oxfffffffff; //clear interupt

//Installing Interupts

MAC7100InstallIRQ( INTC CAN A MB, 0, INTC CANA Handler);

//Configuration Register

MCRA bit.MAXMB = 0xf;

MCRA bit.SUPV

= 1;

= 0;

MCRA bit.MDIS

MCRA bit.HALT

= 0;

PINDATA13 F=0;

}

void init_flexcanB(void) { //RX MB0

//Set Pins G6 and G7 as Peripheral Pins

CONFIG6_G_bit.MODE = 1;

CONFIG7_G_bit.MODE = 1;

//Set Control Register

CTRLB = 0;

CTRLB_bit.RJW = 3;

CTRLB bit.PSEG1 = 2;//

CTRLB bit.PSEG2 = 2;//

CTRLB bit.PROPSEG = 2;//

CTRLB bit.TSYN = 1;

CTRLB bit.PRESDIV = 0;

CTRLB bit.LBUF = 0;

CTRLB_bit.CLK_SRC = 1;

//CTRLB bit.LPB = 1; //Enable Loop back Mod

//Initialize All Message Buffers - in Use

MB0B W0 bit.CODE =0;

MB0B W0 bit.IDE =0;

//Initialize All Message Buffers - 1-31 Not in Use

MB1B W0 =0; MB2B W0 =0; MB3B W0 =0;

MB4BW0 = 0; MB5BW0 = 0; MB6BW0 = 0;

MB7B W0 =0; MB8B W0 =0; MB9B W0 =0;

MB10B W0 = 0; MB11B W0 = 0; MB12B W0 = 0;

MB13B_W0 =0; MB14B_W0 =0; MB15B_W0 =0;

MB16B_W0 = 0; MB17B_W0 = 0; MB18B_W0 = 0;

MB19B_W0 =0; MB20B_W0 =0; MB21B_W0 =0;

MB22B_W0 =0; MB23B_W0 =0; MB24B_W0 =0;

MB25B_W0 =0; MB26B_W0 =0; MB27B_W0 =0;

MB28B_W0 =0; MB29B_W0 =0; MB30B_W0 =0;

MB31BW0 = 0;

//Acceptance Mask Bit

RXGMASKB bit.MI = 0;//all 0 in the mask (dont care)

//Interupt Set up

IMASKB = 0x00000001; //Interupt Mask for MB0

IFLAGB = 0xfffffffff; //clear interupt

```

```

//Installing Interupts

MAC7100InstallIRQ( INTC CAN B MB, 1, INTC CANB Handler);

//Configuration Register

MCRB bit.MAXMB = 0xf;

= 1;

= 0;

MCRB bit.SUPV

MCRB bit.MDIS

MCRB bit.HALT

PINDATA14 F=0;

void INTC CANA Handler (void) {

IFLAGA = 0xfffffffff; //clear interupt

a = MB0A W0 bit.CODE;

b = MB0A W2 bit.DATA0;

c = MB0A_W0_bit.TIME STAMP;

d = MB0A W2 bit.DATA1;

e = MBOA_W2_bit.DATA2;

}

void INTC CANB Handler (void) {

IFLAGB = 0xfffffffff;; //clear interupt

a = MB0B W0 bit.CODE;

b = MB0B W0 bit.TIME STAMP;

a1= MB0B W2 bit.DATA0;

a2= MB0B W2 bit.DATA1;

a3= MB0B W2 bit.DATA2;

a4= MB0B_W2_bit.DATA3;

a5= MB0B_W3_bit.DATA4;

a6= MB0B_W3_bit.DATA5;

a7= MB0B_W3_bit.DATA6;

a8= MB0B W3 bit.DATA7;

if (a1 == d && a3==d&& a5==d && a7==d) e++;

else{

c=1;

}

f++;

d++;

if(d>200)d=0;

MB0B W0 bit.CODE = 0;

MB0B_W1_bit.ID = 0;

MB0B_W0_bit.CODE = 4;

MB0A W1 bit.ID

MB0A_W2_bit.DATA0 = d;

MB0A_W2_bit.DATA1 = 0;

MB0AW2 bit.DATA2 = d;

MB0AW2 bit.DATA3 = 0;

MB0AW3 bit. DATA4 = d;

MB0AW3 bit.DATA5 = 0;

MBOA W3 bit.DATA6 = d;

MB0A W3 bit.DATA7 = 0;

```

```

MBOA_WO_bit.LENGTH= 8;

MB0A_W0_bit.CODE = 0xC;

}

void INTC_PIT1_Handler( void ) {

static unsigned int DispBuffer = 0;

PITFLG |= ( BIT1 ) ; /* clear flag */

DispBuffer ++;

if (DispBuffer>=10) {

DispBuffer=0;

t++;

PINDATA15_F=~PINDATA15_F;

if (t>=100) {

t=0;

d=0;

e=0;

f=0;

}

}

```

| CAN Rate |        | 500kbps |        | 750kbps |        | 1000kbps |        | 1500kbps |        |        | 2000kbps |         |         |         |         |         |

|----------|--------|---------|--------|---------|--------|----------|--------|----------|--------|--------|----------|---------|---------|---------|---------|---------|

| Bus      | Length | 100cm   | 150cm  | 300cm   | 100cm  | 150cm    | 300cm  | 100cm    | 150cm  | 300cm  | 100cm    | 150cm   | 300cm   | 100cm   | 150cm   | 300cm   |

|          | 1      | 358.51  | 362.15 | 363.19  | 535.81 | 535.91   | 533.86 | 698.98   | 695.18 | 697.96 | 1020.95  | 1008.00 | 997.51  | 1296.23 | 1278.44 | 1265.89 |

|          | 2      | 357.52  | 365.00 | 357.50  | 535.64 | 531.78   | 538.25 | 696.15   | 693.94 | 698.29 | 1023.51  | 1007.35 | 999.85  | 1299.09 | 1283.26 | 1262.23 |

|          | 3      | 363.98  | 357.42 | 363.46  | 533.06 | 532.82   | 535.51 | 695.62   | 700.13 | 696.94 | 1021.90  | 1009.85 | 998.16  | 1295.06 | 1283.04 | 1266.21 |

|          | 4      | 364.66  | 363.41 | 362.61  | 538.95 | 536.75   | 538.08 | 694.67   | 696.98 | 697.90 | 1024.14  | 1013.38 | 996.70  | 1300.20 | 1284.60 | 1266.89 |

|          | 5      | 358.66  | 362.07 | 358.57  | 532.82 | 536.66   | 535.50 | 697.38   | 695.55 | 694.61 | 1018.85  | 1008.14 | 997.30  | 1296.66 | 1283.87 | 1266.10 |

|          | 6      | 361.03  | 360.89 | 362.68  | 535.12 | 537.25   | 536.06 | 698.96   | 697.99 | 700.33 | 1022.15  | 1006.56 | 996.42  | 1299.09 | 1279.31 | 1267.10 |

|          | 7      | 359.49  | 362.32 | 362.16  | 534.46 | 537.71   | 537.05 | 696.13   | 700.17 | 698.92 | 1019.53  | 1009.77 | 999.30  | 1297.73 | 1282.33 | 1266.79 |

|          | 8      | 362.61  | 363.68 | 361.00  | 538.32 | 533.71   | 536.94 | 697.97   | 697.41 | 695.73 | 1024.42  | 1007.56 | 1001.35 | 1299.52 | 1281.83 | 1267.12 |

|          | 9      | 358.96  | 361.89 | 363.58  | 536.68 | 535.15   | 534.61 | 695.23   | 697.36 | 699.03 | 1018.37  | 1009.19 | 996.74  | 1296.76 | 1282.08 | 1266.84 |

|          | 10     | 364.33  | 361.12 | 359.96  | 535.84 | 536.02   | 538.45 | 696.66   | 697.44 | 698.26 | 1022.24  | 1010.99 | 995.76  | 1299.94 | 1285.54 | 1263.79 |

|          | 11     | 362.17  | 364.91 | 360.16  | 537.66 | 538.24   | 536.76 | 695.89   | 696.22 | 695.27 | 1022.85  | 1008.49 | 997.21  | 1295.00 | 1283.63 | 1264.31 |

|          | 12     | 360.36  | 363.44 | 361.81  | 533.40 | 536.00   | 536.25 | 698.09   | 699.75 | 695.57 | 1020.47  | 1011.53 | 997.78  | 1299.68 | 1283.16 | 1264.50 |

|          | 13     | 365.23  | 364.80 | 357.91  | 533.78 | 536.64   | 531.81 | 696.48   | 697.27 | 700.59 | 1023.79  | 1012.68 | 995.59  | 1296.49 | 1280.39 | 1261.88 |

|          | 14     | 359.89  | 358.77 | 361.15  | 533.84 | 538.43   | 535.43 | 696.61   | 699.56 | 699.75 | 1019.57  | 1008.90 | 995.50  | 1295.61 | 1279.81 | 1263.47 |

| Runs     | 15     | 360.45  | 360.61 | 361.39  | 535.28 | 537.49   | 534.62 | 699.12   | 697.31 | 696.28 | 1024.32  | 1008.85 | 997.61  | 1298.04 | 1283.61 | 1264.51 |

| - ₹      | 16     | 364.08  | 363.27 | 359.79  | 539.80 | 531.88   | 535.96 | 698.42   | 696.01 | 697.95 | 1022.19  | 1007.10 | 994.08  | 1296.53 | 1284.17 | 1263.32 |

|          | 17     | 362.52  | 359.85 | 364.04  | 536.06 | 536.66   | 535.97 | 699.47   | 695.40 | 699.68 | 1021.55  | 1007.48 | 998.90  | 1298.86 | 1277.62 | 1265.30 |

|          | 18     | 359.98  | 361.32 | 362.74  | 534.20 | 534.66   | 533.78 | 696.96   | 697.50 | 695.20 | 1021.06  | 1006.45 | 995.46  | 1297.54 | 1282.61 | 1265.52 |

|          | 19     | 363.30  | 363.08 | 361.95  | 534.60 | 537.76   | 534.69 | 694.14   | 698.01 | 696.34 | 1022.02  | 1009.24 | 996.46  | 1299.92 | 1283.06 | 1263.15 |

|          | 20     | 362.30  | 364.44 | 360.53  | 536.76 | 537.92   | 533.83 | 695.37   | 694.10 | 700.39 | 1019.75  | 1007.65 | 999.56  | 1297.20 | 1280.17 | 1262.59 |

|          | 21     | 362.90  | 365.50 | 360.25  | 537.58 | 537.50   | 534.37 | 693.32   | 696.44 | 700.35 | 1020.95  | 1011.96 | 999.18  | 1297.89 | 1281.72 | 1269.36 |

|          | 22     | 363.88  | 363.40 | 362.55  | 534.44 | 533.54   | 532.51 | 698.62   | 695.56 | 698.07 | 1019.88  | 1009.89 | 995.74  | 1297.97 | 1284.32 | 1262.43 |

|          | 23     | 362.40  | 362.34 | 362.66  | 535.22 | 535.45   | 535.87 | 698.68   | 695.47 | 697.85 | 1021.74  | 1008.41 | 997.55  | 1298.48 | 1283.05 | 1268.75 |

|          | 24     | 360.55  | 361.45 | 359.85  | 536.49 | 534.93   | 533.16 | 695.97   | 698.77 | 696.44 | 1019.85  | 1007.55 | 994.08  | 1295.59 | 1280.10 | 1267.81 |

|          | 25     | 360.39  | 363.32 | 359.16  | 535.27 | 533.87   | 532.55 | 696.83   | 694.96 | 700.51 | 1021.66  | 1011.39 | 999.58  | 1296.18 | 1279.45 | 1263.52 |

|          | 26     | 359.22  | 361.77 | 359.88  | 533.17 | 534.99   | 536.20 | 694.14   | 695.80 | 694.26 | 1021.48  | 1008.88 | 998.33  | 1296.06 | 1280.60 | 1266.24 |

|          | 27     | 358.95  | 360.94 | 364.93  | 534.59 | 535.89   | 534.29 | 696.46   | 700.92 | 694.11 | 1023.33  | 1008.49 | 994.12  | 1297.07 | 1282.74 | 1266.47 |

|          | 28     | 360.00  | 363.47 | 362.58  | 533.38 | 532.62   | 533.62 | 696.16   | 700.46 | 695.58 | 1020.59  | 1010.72 | 994.96  | 1295.91 | 1280.35 | 1263.97 |

|          | 29     | 360.79  | 359.11 | 361.63  | 535.73 | 536.78   | 538.84 | 700.58   | 700.05 | 695.63 | 1019.57  | 1010.31 | 998.70  | 1295.91 | 1280.94 | 1266.35 |

|          | 30     | 359.54  | 359.91 | 361.34  | 532.13 | 537.92   | 536.33 | 697.92   | 698.18 | 698.07 | 1024.98  | 1005.79 | 999.39  | 1299.19 | 1283.47 | 1266.73 |

|          | ERAGE  | 361.29  | 362.19 | 361.37  | 535.34 | 535.76   | 535.37 | 696.90   | 697.33 | 697.53 | 1021.59  | 1009.09 | 997.30  | 1297.51 | 1281.98 | 1265.30 |

| STI      | D DEV  | 2.11    | 1.97   | 1.81    | 1.87   | 1.93     | 1.82   | 1.76     | 1.97   | 2.02   | 1.77     | 1.90    | 1.90    | 1.58    | 1.98    | 1.98    |

```

// Include Files

#include <intrinsics.h>

#include <stdio.h>

#include <iolpc2148.h>

#include "SPI FNs.h" // Basic functions to read and write the MAX3420E and MAX3421E regs. #include "MAX3421E.h" // MAX3421E registers and bit names

#include "MAX3421E.h" // MAX3421E registers and bit names #include "Keil_MCB2130.h" // IO assignments unique to the Keil board

// MAX3421E registers and bit names

// Function Declaration

extern void init serial(void); // Set up the serial port for connection to PC running

terminal program

// Prototypes

BYTE CTL_Write_ND(BYTE *pSUD); // Do a USB CONTROL-Write with no data stage void waitframes(BYTE num); // Wait num frames (SOF or KA interrupts)

BYTE Send Packet(BYTE token, BYTE endpoint);

BYTE CTL Read(BYTE *pSUD); // Setup-IN-Status.

BYTE IN Transfer(BYTE endpoint, WORD INbytes); // Called by CTL Read for the data stage

void initialize 3420(void);

void service_irqs(void); // This function is in '3420_HIDKB_INT_EVK.C' module void boardtest(void); // Checks buttons and lights

void initialize_ARM_Interrupts(void);

void detect_device(void); // Hangs until device detected

void enumerate_device(void); // Send a bunch of CONTROL requests and reports over serial

void wait for disconnect(void);

BYTE myIN(WORD INbytes);

//******

*********

// Global Variables

//**************************

unsigned int time1;

unsigned char temp, sync=0;

unsigned long sendtime, ttime, runtime, restime, total, correct;

unsigned char pksize = 64;

unsigned char test[64];

static WORD VID, PID, nak count, IN nak count, HS nak count;

static unsigned int last transfer size;

unsigned volatile long timeval;

// incremented by timer0 ISR

WORD inhibit send;

// Definitions

//****************************

#define ESC putchar(0x1B) // ESC character for sending VT100 escape codes.

// Set transfer bounds

#define NAK LIMIT 200

#define RETRY_LIMIT 3

#define t1 1000

// IRQ Handler

\ensuremath{//} IRQ exception handler. Calls the interrupt handlers.

#pragma vector=IRQV

__irq __arm void irq_handler (void)

void (*interrupt_function)();

```

```

unsigned int vector;

// Get interrupt vector.

vector = VICVectAddr;

interrupt function = (void(*)()) vector;

if(interrupt function != NULL)

interrupt_function(); // Call vectored interrupt function.

else

{

VICVectAddr = 0;

// Clear interrupt in VIC.

// Interrupt Handlers

//**************************

//Dummy interrupt handler, called as default in irqHandler() if no other

//vectored interrupt is called.

static void DefDummyInterrupt()

// Timer Counter 0 Interrupt executes each 20ms @ 48 MHz CPU Clock

// Increment counters timeval for general program use.

void tc0 (void)

if(time1 > 0)

time1--;

sendtime++;

runtime++;

TOIR = 1; // Clear interrupt flag

VICVectAddr = 0; // Dummy write to indicate end of interrupt service

// L6_OFF // for the scope

// Timer Counter 1 Interrupt executes each 50ms @ 48 MHz CPU Clock

// Checks the start/stop button, clears inhibit_send if pressed.

// Also increments blinkcount and blinks the D4 led when at limit.

//

void tcl (void)

T1IR

// Clear interrupt flag

VICVectAddr = 0;

// Dummy write to indicate end of interrupt service

// L7 OFF // for the scope

// EINTO Interrupt handler--MAX3420E INT pin

void INT3420 (void)

service_irqs();

// Clear EINTO interrupt flag (b0)

= 1;

VICVectAddr = 0;

// Dummy write to indicate end of interrupt service

// EINT2 Interrupt Handler--MAX3421E INT pin (not used, just an example)

void INT3421 (void)

= 4; // Clear EINT2 interrupt flag (b0)

EXTINT

// Dummy write to indicate end of interrupt service

VICVectAddr = 0;

// Initialize Interrupts

void initialize ARM Interrupts(void)

// Set up the Timer Counter 0 Interrupt

// Used to blink the activity light

```

```

TOMR0 = 48000; //960000;

// Match Register 0: 20 msec(50 Hz) with 48 MHz clock

TOMCR = 3;

// Match Control Reg: Interrupt(b0) and Reset(b1) on MR0

TOTCR = 1;

// Timer0 Enable

VICVectAddr1 = (unsigned long)tc0; // Use slot 1, second highest vectored IRQ priority.

VICVectCntl1 = 0x20 | 4;

// 0x20 interrupt enable bit, 0x04 TIMERO channel number

// Enable TimerO Interrupt bit 4 (1 sets the bit)

VICIntEnable = 0 \times 000000010;

// Set up the Timer Counter 1 Interrupt

// Used to check the send/stop button PB5

// Match Register 0: 100 msec (10Hz) with 48 MHz clock

T1MR0 = 4800000;

T1MCR = 3;

// Match Control Reg: Interrupt(b0) and Reset(b1) on MR0

T1TCR = 1;

// Timer1 Enable

VICVectAddr3 = (unsigned long)tc1;

// Use slot 3, lowest vectored IRQ priority in this app

VICVectCntl3 = 0x20 | 5;

// 0x20 interrupt enable bit, 0x05 TIMER5 channel number

// Enable Timerl Interrupt bit 5 (1 sets the bit)

VICIntEnable = 0 \times 000000020;

// Set up the EINTO (P0.16) interrupt (MAX3420E Interrupt pin)

EXTMODE

| = 0 \times 01;

// EINTO is edge-sensitive

EXTPOLAR

| = 0 \times 01;

// positive edge

= 1;

// clear the IRQ which may have been set

VICVectAddr0 = (unsigned long)INT3420; // Use slot 0, highest vectored IRQ priority.

VICVectCntl0 = 0x20 | 14; // 0x20 interrupt enable bit, 14(D) is EINTO channel number

VICIntEnable = 0 \times 00004000;

// Enable EINTO interrupt bit 14 (1 sets the bit)

// Set up the EINT2 (P0.15) interrupt (MAX3421E Interrupt pin) -- not used, just an example.

// Set for pos-edge

Hwreg(rPINCTL, (bmFDUPSPI|bmPOSINT)); //INTLEVEL=0, POSINT=1 for pos edge interrupt pin

EXTMODE \mid = 0x04; // EINT2 is edge-sensitive

0x04; // positive edge

= 4; // clear

| = 0x04;

EXTPOLAR

// clear the IRQ which may have been set

EXTINT

VICVectAddr2 = (unsigned long)INT3421;  // Use slot 2

\label{eq:VICVectCntl2} VICVectCntl2 = 0x20 \ | \ 16; \\ \hspace*{0.2cm} // \ 0x20 \ interrupt \ enable \ bit, \ 16(D) \ EINT2 \ channel \ number

VICIntEnable = 0x00010000;

// Enable EINT2 interrupt bit 16 (1 sets the bit)

// Task Functions

//**************************

void task1(void){

time1=t1;

if(temp){L1 ON;temp=0;}

else{L1_OFF;temp=1;}

// Main Function

void main (void)

init PLL();

init_IO();

init_serial();

initialize ARM Interrupts();

initialize 3420();

time1=t1;

__enable_interrupt();

// INITIALIZE MAX3421

//

Hwreg(rPINCTL, (bmFDUPSPI|bmPOSINT)); // MAX3421E: Full duplex mode, INTLEVEL=0, POSINT=1 for pos

edge interrupt pin

Reset_Host();

// Jan07_2008: Moved Reset_Host after MAX3421 is put in full duplex

// all LEDS off

Pwreg(rIOPINS1,0x00);

// seven-segs off

Hwreg(rIOPINS1,0x00);

// and Vbus OFF (in case something already plugged in)

Hwreg(rIOPINS2,0x00);

```

```

// Cycle power. This section was added after observing that some USB thumb drives can get

// into a locked-up state that a USB bus reset does not clear. This behavior was observed

// by starting this program with a thumb drive already plugged in.

//

time1=t1;

// timeval clicks every 20 msec

while(time1 > 500);

VBUS ON

// Vbus back ON

//Pwreg(rEPIEN, Prreg(rEPIEN) | bmIN3BAVIE);

int i=0, cc=0;

int qq=0;

while(1){

ESC; printf("[2J");

// clear the VT100 screen

ESC; printf("[H");

// reset cursor

printf("----\n");

printf("Maxim USB Laboratory\n");

printf("----\n");

detect device();

waitframes(200);

// Some devices require this

enumerate_device();

for(i=0;i<pksize;i++) {test[i]=i;}</pre>

for(i=0;i<600;i++) { XfrData[i]=0;}

printf("Start\r\n");

ttime=0;

runtime=0:

total=0;

correct=0;

Pwritebytes (rEP2INFIFO, pksize, test);

Pwreg(rEP2INBC,pksize);

Pwritebytes (rEP2INFIFO, pksize, test);

Pwreg(rEP2INBC,pksize);

for(cc=0;cc<500;cc++){

//sendtime=0;

qq=IN_Transfer(2,512);

//ttime=ttime+sendtime;

total+=last_transfer_size;

for(i=0;i<512;i++){

if(XfrData[i]==i%64) correct++;

}

restime=runtime;

printf("Run Time:\t\t%d ms\r\n", restime);

printf("Send Time:\t\t%d ms\r\n",ttime);

printf("Total Bits:\t\t%d bits\r\n",total*8);

printf("Correct:\t\t%d bits\r\n",correct*8);

printf("Correct %%:\t\t%3.2f %%\r\n",((float)correct)/((float)total)*100);

printf("Data Rate:\t\t%d bits/sec\r\n",total*8/ttime*1000);

printf("uController %%:\t\t%3.2f %%\r\n",((float)ttime)/((float)restime)*100);

printf("Done\r\n");

wait for disconnect();

```

```

// Reset Host

void Reset Host(void)

Hwreg(rUSBCTL,bmCHIPRES); // chip reset This stops the oscillator Hwreg(rUSBCTL,0x00); // remove the reset

while(!(Hrreg(rUSBIRQ) & bmOSCOKIRQ)); // hang until the PLL stabilizes

//*****************************

// Detect Device

void detect device(void)

int busstate:

// Activate HOST mode & turn on the 15K pulldown resistors on D+ and D-

Hwreg(rMODE,(bmDPPULLDN|bmDMPULLDN|bmHOST)); // Note--initially set up as a FS host (LOWSPEED=0)

Hwreg(rHIRQ,bmCONDETIRQ); // clear the connection detect IRQ

HL3 OFF;

printf("Waiting for device connect\n\n");

// See if anything is plugged in. If not, hang until something plugs in

Hwreg(rHCTL,bmSAMPLEBUS);

// update the JSTATUS and KSTATUS bits

busstate = Hrreg(rHRSL);

// read them

busstate &= (bmJSTATUS|bmKSTATUS); // check for either of them high

while (busstate==0);

if (busstate==bmJSTATUS)

// since we're set to FS, J-state means D+ high

// make the MAX3421E a full speed host

Hwreg(rMODE, (bmDPPULLDN|bmDMPULLDN|bmHOST|bmSOFKAENAB));

readout(0xf);

if (busstate==bmKSTATUS) // K-state means D- high

// make the MAX3421E a low speed host

Hwreg (rMODE, (bmDPPULLDN | bmDMPULLDN | bmHOST | bmLOWSPEED | bmSOFKAENAB));

readout (0x5);

}

// Enum Dev

void enumerate_device(void)

static BYTE HR, iCONFIG, iMFG, iPROD, iSERIAL;

static WORD TotalLen, ix;

static BYTE len,type,adr,pktsize;

// SETUP bytes for the requests we'll send to the device

static BYTE Set_Address_to_7[8] = {0x00,0x05,0x07,0x00,0x00,0x00,0x00,0x00};

static BYTE Get_Descriptor_Device[8] = {0x80,0x06,0x00,0x01,0x00,0x00,0x00,0x00};

static BYTE Get Descriptor Config[8] = \{0x80,0x06,0x00,0x02,0x00,0x00,0x00,0x00\};

// Get Descriptor-String template. Code fills in idx at str[2].

static BYTE str[8] = \{0x80,0x06,0x00,0x03,0x00,0x00,0x40,0x00\};

// Issue a USB bus reset

;//printf("Issuing USB bus resetn");

while(Hrreg(rHCTL) & bmBUSRST); // Wait for the bus reset to complete

// Wait some frames before programming any transfers. This allows the device to recover from

// the bus reset.

waitframes(200);

// Get the device descriptor.

```

```

maxPacketSize = 8;

// only safe value until we find out

Hwreq(rPERADDR,0);

// First request goes to address 0

Get_Descriptor_Device[7]=0;

://printf/""

// wLengthL

// wLengthH

;//printf("First 8 bytes of Device Descriptor ");

if(print error(HR)) return; // print error() does nothing if HRSL=0, returns the 4-bit HRSL.

;//printf("(%u/%u NAKS)\n",IN_nak_count,HS_nak_count);

// Show NAK count for data

stage/status stage

maxPacketSize = XfrData[7];

for (ix=0; ix<last_transfer_size;ix++)</pre>

;//printf("%02X ",(BYTE*)XfrData[ix]);

;//printf("\n");

;//printf("EPO maxPacketSize is %02u bytes\n", maxPacketSize);

// Issue another USB bus reset

;//printf("Issuing USB bus resetn");

while(Hrreg(rHCTL) & bmBUSRST); // Wait for the bus reset to complete

waitframes (200);

// Set_Address to 7 (Note: this request goes to address 0, already set in PERADDR register).

;//printf("Setting address to 0x07\n");

HR = CTL_Write_ND(Set_Address_to_7);  // CTL-Write, no data stage

if(print error(HR)) return;

waitframes(30);

// Device gets 2 msec recovery time

Hwreg(rPERADDR,7);

// now all transfers go to addr 7